ShenZhen ChipSourceTek Technology Co., Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

#### **Features**

- Broadband frequency range: 0.4 to 6.0GHz

- Only one supply voltage needed

- MIPI RFFE V2.1 compatible Interface

- Compact 1.1mm x 1.1mm x 0.5mm LGA-9 package,

MSL3

#### **Applications**

2G/3G/4G/5G antenna TRX switch

#### **Description**

The LX8648M is a CMOS silicon-on-insulator (SOI),

SP4T transmitting and receiving switch. The high linearity performance and low insertion loss makes the device an ideal choice for GSM/WCDMA/LTE handset and data card applications.

The LX8648M is compatible with MIPI RFFE V2.1 control, which is a key requirement for many cellular transceivers. This part is packaged in a compact 1.1mm x 1.1mm x 0.5mm LGA package, which allows for a small solution size with no need for external DC blocking capacitors (when no external DC is applied to the device ports).

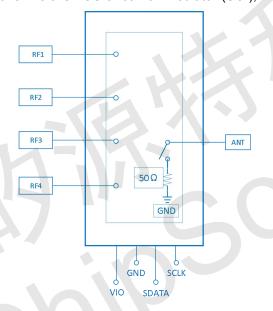

Figure 1. Functional Block Diagram and Pin Configuration Top View

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

## **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

#### **Function Characteristics**

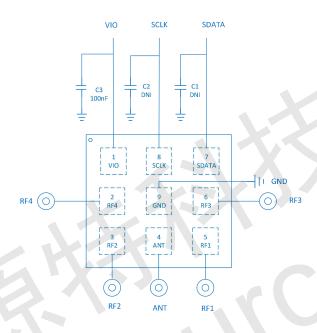

Figure 2. LX8648M Application Circuit

**Table 1. Pin Descriptions**

| NO. | Name         | Description    | NO. | Name  | Description |

|-----|--------------|----------------|-----|-------|-------------|

| 1   | VIO          | Supply Voltage | 6   | RF3   | RF Port3    |

| 2   | RF4          | RF Port4       | 7   | SDATA | RFFE Data   |

|     |              |                | /   | SDATA | Bus         |

| 3   | RF2 RF Port2 |                | 8   | SCLK  | RFFE Clock  |

|     |              |                | 0   | SOLK  | Bus         |

| 4   | ANT          | Antenna Port   | 9   | GND   | Ground      |

| 5   | RF1          | RF Port1       |     |       |             |

Table 2. Register\_0 Truth Table for RF Operating Modes

| Mode                  |    |    |    | Regis | ter_0 |    |    |    |

|-----------------------|----|----|----|-------|-------|----|----|----|

|                       | D7 | D6 | D5 | D4    | D3    | D2 | D1 | D0 |

| All RF Paths Isolated | 0  | 0  | 0  | 0     | 0     | 0  | 0  | 0  |

| RF1 ON                | 0  | 0  | 0  | 0     | 0     | 0  | 0  | 1  |

| RF2 ON                | 0  | 0  | 0  | 0     | 0     | 0  | 1  | 0  |

| RF3 ON                | 0  | 0  | 0  | 0     | 0     | 1  | 0  | 0  |

| RF4 ON                | 0  | 0  | 0  | 0     | 1     | 0  | 0  | 0  |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

#### **Electrical Characteristics**

#### **Table 3. Absolute Maximum Ratings**

| Parameter                          | Symbol                | Min  | Max | Unit       | Condition                                              |

|------------------------------------|-----------------------|------|-----|------------|--------------------------------------------------------|

| Supply Voltage                     | $V_{IO}$              | -0.3 | 2.5 |            | TA=25℃                                                 |

| RFFE Bus Voltage (SDATA,           | $V_{l}$               | -0.3 | 2.5 | V          | TA=25℃                                                 |

| SCLK)                              |                       |      |     |            |                                                        |

| Max RF Input Power                 | $P_{IN}$              |      | 38  | dBm        | F <sub>0</sub> =950MHz, 20% DC, V <sub>IO</sub> =1.8V, |

| (ANT to RF1/2/3/4)                 |                       |      |     |            | ZO=50Ω,                                                |

|                                    |                       |      |     |            | TA=25℃                                                 |

| Device Operating Temperature       | $T_OP$                | -40  | 90  | $^{\circ}$ |                                                        |

| Device Storage Temperature         | $T_{STG}$             | -55  | 150 |            |                                                        |

| Electrostatic Discharge(All Pins)  | V <sub>ESD(HBM)</sub> | 1    |     | kV         | Human Body Model                                       |

| Electrostatic Discharge(All Filis) | $V_{\rm ESD(CDM)}$    | 1    |     |            | Charged Device Model                                   |

#### Note:

Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

**Table 4. Recommended Operating Conditions**

| Parameter                          | Symbol          | MIN     | TYP  | MAX     | Unit |

|------------------------------------|-----------------|---------|------|---------|------|

| Operating Frequency                | F <sub>0</sub>  | 0.4     |      | 6.0     | GHz  |

| Supply Voltage                     | V <sub>IO</sub> | 1.65    | 1.80 | 1.95    |      |

| RFFE Bus Voltage(SDATA, SCLK) High | V <sub>IH</sub> | 0.8*VIO | VIO  | VIO     | V    |

| RFFE Bus Voltage(SDATA, SCLK) Low  | V <sub>IL</sub> | 0       | 0    | 0.2*VIO |      |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

**Table 5. Nominal Operating Parameters**

| Parameter              | Symbol   | Specification |           | Unit    | Condition                                |                                          |

|------------------------|----------|---------------|-----------|---------|------------------------------------------|------------------------------------------|

|                        |          | MIN           | TYP       | MAX     |                                          |                                          |

| Normal Condition       | H=1.8V   | , VIL=0V,     | PIN=0     | dBm, VS | SWR=1:1, TA=25℃, Unless Otherwise Stated |                                          |

|                        |          | DC P          | erforman  | ices    |                                          |                                          |

|                        | 1.0      |               | 80        | 100     |                                          | Active State                             |

| Supply Current         | liO      |               | 6         | 10      | μA                                       | Low Power State                          |

|                        |          | Timin         | g Perforr | nances  | l                                        |                                          |

| Switching Time (One    | TOVA     |               | _         | _       |                                          | Cuitabias CMD 500/ CCLK to 000/ /400/ DE |

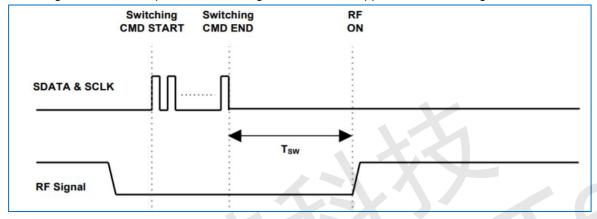

| On Path to Another)    | TSW      |               | 2         | 3       |                                          | Switching CMD 50% SCLK to 90%/10% RF     |

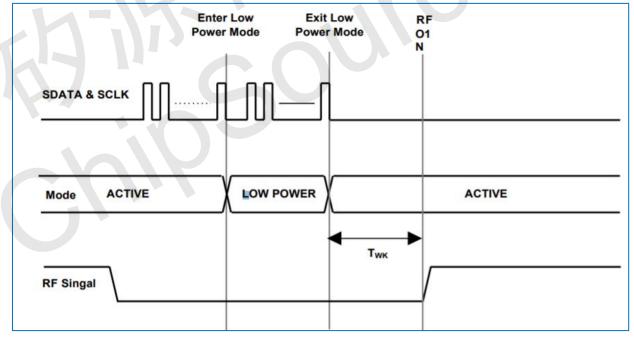

| Wakaup Timo            | TWK      |               | 5         | 10      |                                          | End of Low Power State                   |

| Wakeup Time            | IVVK     |               | 5         | 10      | 110                                      | 50% SCLK to 90% RF                       |

| Turn On Time           | TON      |               |           | 20      | μs                                       | Cold Start, 50% VIO to 90% RF            |

| VIO Reset Time         | TVIO_RST | 10            |           |         |                                          | VIO Off to it starts to re-power up      |

|                        |          | RF P          | erforman  | ces     |                                          |                                          |

|                        |          |               | 0.40      | 0.45    |                                          | F0=0.4 to 1.0GHz                         |

| Insertion Loss         |          |               | 0.45      | 0.50    |                                          | F <sub>0</sub> =1.0 to 2.0GHz            |

| (ANT to                |          | $\Lambda$     | 0.50      | 0.55    |                                          | F0=2.0 to 3.0GHz                         |

| RF1/2/3/4)             | IL       |               | 0.55      | 0.65    |                                          | F0=3.0 to 3.8GHz                         |

|                        |          |               | 0.65      | 0.90    |                                          | F0=4.8 to 6.0GHz                         |

|                        |          | 40            | 42        |         |                                          | F0=0.4 to 1.0GHz                         |

| Isolation              |          | 38            | 40        |         |                                          | F <sub>0</sub> =1.0 to 2.0GHz            |

| (ANT to RF1/2/3/4)     | ISO      | 33            | 35        |         |                                          | F <sub>0</sub> =2.0 to 3.0GHz            |

| (71111 10 111 1121014) |          | 28            | 30        |         | dB                                       | F0=3.0 to 3.8GHz                         |

|                        |          | 21            | 24        |         |                                          | F <sub>0</sub> =4.8 to 6.0GHz            |

| Input Return Loss      | RL       | 12            | 15        |         |                                          | F0=0.4 to 2.7GHz                         |

| (ANT to RF1/2/3/4)     | IVE.     | 10            | 13        |         |                                          | F <sub>0</sub> =2.7 to 6.0GHz            |

| Input 0.1dB            |          |               |           |         |                                          |                                          |

| Compression            |          |               |           |         |                                          |                                          |

| Point (ANT to          | P0.1dB   |               | 38        |         | dBm                                      | F0=950MHz, 20% DC                        |

| RF1/2/3/4)             |          |               |           |         |                                          |                                          |

| 2nd Order              |          |               | -90       | -85     |                                          | F0=950MHz @26dBm                         |

| Harmonic (ANT to       | 2F0      |               | -85       | -80     |                                          | F0=950MHz @35dBm                         |

| RF1/2/3/4)             | 0        |               | -85       | -80     |                                          | F0=1800MHz @32dBm                        |

| 3rd Order              |          |               | -92       | -88     |                                          | F0=950MHz @26dBm                         |

| Harmonic (ANT to       | 3F0      |               | -85       | -80     | dBc                                      | F0=950MHz @35dBm                         |

| RF1/2/3/4)             | 5. 0     |               | -85       | -80     |                                          | F0=1800MHz @32dBm                        |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

### LX8648M

#### 0.4 to 6.0GHz SP4T Switch with MIPI

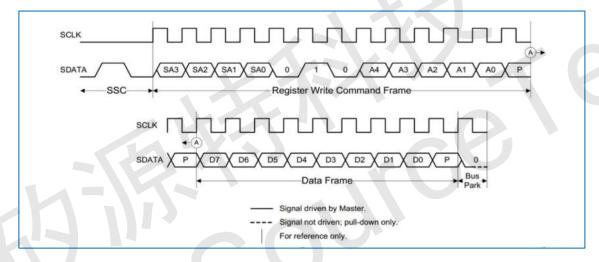

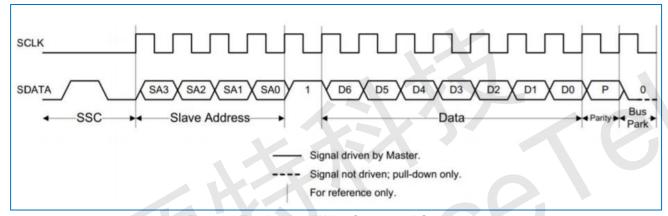

#### **MIPI RFFE Read and Write Timing**

MIPI RFFE supports the following Command Sequences:

- Register Write

- Register Read

- Register 0 Write

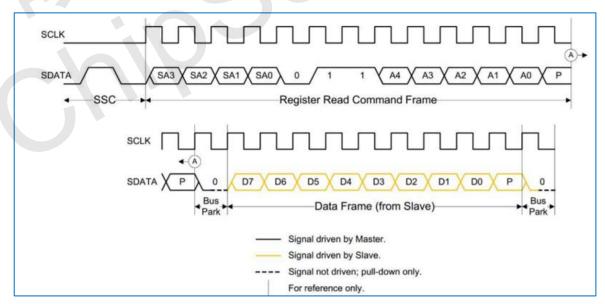

Figure 3 and Figure 4 illustrate the timing diagrams for register write command sequence and read command sequence, respectively. Figure 5 describes the Register\_0 write command sequence. In the below timing figures, SA[3:0] is the slave address. A[4:0] is the register address. D[7:0] is the data. "P" is a parity bit.

Figure 3 Register Write Command Sequence

Figure 4 Register Read Command Sequence

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

Figure 5 shows the Register\_0 Write Command Sequence. The Command Sequence starts with an SSC, followed by the Register 0 Write Command Frame containing the Slave address, a logic '1' (to denote the command type and address), and a only seven- bit word to be written into Register 0. The Command Sequence ends with a Bus Park Cycle.

Figure 5 Register\_0 Write Command Sequence

Other information such as MIPI RFFE USID programming sequence, MIPI RFFE bus specifications, etc. can be referred to the MIPI Alliance Specification for RF Front-End Control Interface (RFFE), V2.1.

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

### **Register Definition**

#### **Table 6. Register Definition Table**

| Register | Register Name | Data  | R/W      | Function              | Description                         | Default   | BROADC     | Trigger  |

|----------|---------------|-------|----------|-----------------------|-------------------------------------|-----------|------------|----------|

| Address  |               | Bits  |          |                       |                                     |           | AST_ID     | support  |

|          |               |       |          |                       |                                     |           | support    |          |

| 0x00     | REGISTER_0    | 7:0   | R/W      | RF Control            | Register_0 truth Table:             | 0x00      | No         | Yes      |

|          |               |       |          |                       | Table 2                             |           |            |          |

|          |               | 7     | R/W      | PWR_MODE_1            | 0b0: Normal Operation Mode          | 0b0       | Yes        | No       |

|          |               |       |          |                       | Write Value:0b0, Read               |           |            |          |

| 0x1C     | PM_TRIG       |       |          |                       | Value:0b0 0b1: Low Power            |           |            |          |

|          |               |       |          |                       | Mode                                |           |            |          |

|          |               |       |          |                       | Write Value:0b1, Read               |           |            |          |

|          |               |       |          |                       | Value:0b1                           |           |            |          |

|          |               | 6     | R/W      | PWR_MODE_0            | 0b0: Normal Operation               | 0b0       |            |          |

|          |               |       |          |                       | (ACTIVE) 0b1: Reset all             |           |            |          |

|          |               |       |          |                       | registers to default settings       |           |            |          |

|          |               |       |          |                       | (STARTUP)                           |           |            |          |

|          |               |       |          | $\wedge$              | Write value: 0b1, Read              |           |            |          |

|          |               |       |          |                       | Value: 0b0                          |           |            |          |

|          |               | 5     | R/W      | Trigger_Mask_2        | 0b0: Trigger_2 enabled              | 0b0       | No         | No       |

|          |               |       |          |                       | 0b1: Trigger_2 disabled             | 000       | INO        | INO      |

|          |               | 4     | R/W      | Trigger_Mask_1        | 0b0: Trigger_1 enabled              | 0b0       | No         | No       |

|          |               |       |          |                       | 0b1: Trigger_1 disabled             | 000       | INO        | INO      |

|          |               | 3     | R/W      | Trigger_Mask_0        | 0b0: Trigger_0 enabled              | 0b0       | No         | No       |

|          |               |       |          |                       | 0b1: Trigger_0 disabled             | 000       | 110        | 110      |

|          |               | Note  | e: If an | y one of the three    | Trigger Masks is set to a logic '   | 1' the co | orrespond  | ding     |

|          |               |       |          |                       | se data written to a register ass   | ociated   | with the   | Trigger  |

|          |               |       |          | tly to the destinatio | •                                   |           |            |          |

|          |               |       |          |                       | k is enabled (via a logic '0'), inc | oming o   | data is wr | itten to |

|          |               |       |          | v register, and       |                                     | _         |            |          |

|          |               | the o | destina  | ation register is und | changed until its corresponding     | Trigger   | is assert  | ed.      |

|          |               |       |          |                       | 0b0: Keep its associated            |           |            |          |

|          |               | _     |          |                       | destination registers               |           |            |          |

|          |               | 2     | W        | Trigger_2             | unchanged                           | 0b0       | Yes        | No       |

|          |               |       |          |                       | 0b1: Load its associated            |           |            |          |

|          |               |       |          |                       | destination registers with          |           |            |          |

|          |               |       |          |                       | the data in the parallel            |           |            |          |

|          |               |       |          |                       | shadow register, provided           |           |            |          |

|          |               |       |          |                       | Trigger_Mask_2 is                   |           |            |          |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co. , Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

|      | O-TOIVI    |     |     |             | 0.4 to 0.0GHZ 3F41         | OWILL | II WILLI | 17111 1 |

|------|------------|-----|-----|-------------|----------------------------|-------|----------|---------|

|      |            |     |     |             | disabled(Logic '0')        |       |          |         |

|      |            |     |     |             |                            |       |          |         |

|      |            |     |     |             |                            |       |          |         |

|      |            |     |     |             |                            |       |          |         |

|      |            |     |     |             |                            |       |          |         |

|      |            |     |     |             |                            |       |          |         |

|      |            |     |     |             | 0b0: Keep its associated   |       |          |         |

|      |            |     |     |             | destination registers      |       |          |         |

|      |            | 1   | W   | Trigger_1   | unchanged                  | 0b0   | Yes      | No      |

|      |            |     |     | 33 =        | 0b1: Load its associated   |       |          |         |

|      |            |     |     |             | destination registers with |       |          |         |

|      |            |     |     |             | the data in the parallel   |       |          |         |

|      |            |     |     |             | shadow register, provided  |       |          |         |

|      |            |     |     |             | Trigger_Mask_1 is          |       |          |         |

|      |            |     |     |             | disabled(Logic '0')        |       |          |         |

|      |            |     |     |             | 0b0: Keep its associated   |       |          |         |

|      |            |     |     |             | destination registers      |       |          |         |

|      |            | 0   | W   | Trigger_0   | unchanged                  | 0b0   | Yes      | No      |

|      |            |     |     |             | 0b1: Load its associated   |       |          |         |

|      |            |     |     |             | destination registers with |       |          |         |

|      |            |     |     |             | the data in the parallel   |       |          |         |

|      |            |     |     |             | shadow register, provided  |       |          |         |

|      |            |     |     |             | Trigger_Mask_0 is          |       |          |         |

|      | <i>\</i>   |     |     |             | disabled(Logic '0')        |       |          |         |

| 0x1D | PRODUCT_ID | 7:0 | R   | PRODUCT_ID  | Product Number             | 0x72  | No       | No      |

| 0x1E | MANUFACTU  | 7:0 | R   | MANUFACTURE | Lower eight bits of MIPI   | 0x78  | No       | No      |

|      | RER_ID     |     |     | R_ID[7:0]   | registered                 |       |          |         |

|      | -> W 1     |     |     |             | Manufacturer ID            |       |          |         |

| 0x1F | MAN_USID   | 7:6 | R   | RESERVED    |                            | 0b00  | No       | No      |

|      |            | 5:4 | R   | MANUFACTURE | Upper two bits of MIPI     | 0x2   | No       | No      |

|      |            |     |     | R_ID[9:8]   | registered                 |       |          |         |

|      |            |     |     |             | Manufacturer ID            |       |          |         |

|      |            | 3:0 | R/W | USID        | Unique Slave Address       | 0x8   | No       | No      |

|      |            |     |     |             |                            |       |          |         |

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

#### **MIPI RFFE Operating Sequences**

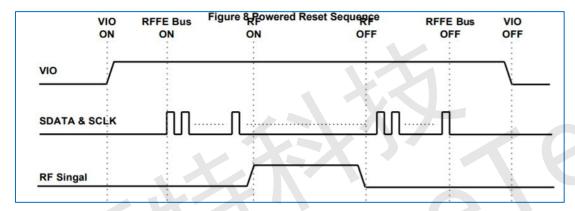

Here are some recommendations for MIPI RFFE operating sequences to prevent the device from damage.

- 1) Basic Operational Sequences

- Power On -- Apply Supply (VIO)-> Apply MIPI RFFE Bus (SCLK & SDATA) -> Apply RF Signal

- Power Off -- Remove RF Signal-> Remove MIPI RFFE Bus (SCLK & SDATA)->Remove Supply (VIO)

Figure 6 Basic Power On and Power Off Sequence

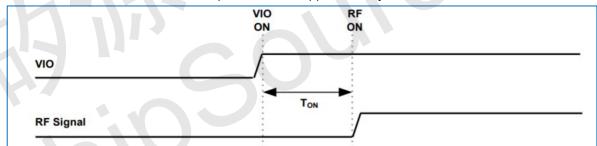

2) There shall be at least TON before RF power can be applied to any RF Path

Figure 7 Supply and RF Signal On Sequence

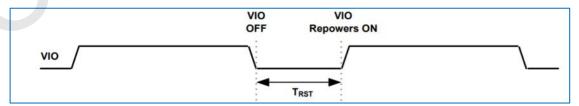

3) Once VIO is off, there shall be at least TRST before VIO is allowed to repower on again.

Figure 8 Supply and RF Signal On Sequence

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

4) If RF signal is to be switched from one RF path to another or some paths to others, RF signal shall not be applied during such switching events to protect the devices. Hence, RF signal shall be removed before the switching command is implemented. RF signal shall not be applied before waiting at least TSW.

Figure 9 RF Path Switching Sequence

5) RF Signal shall not be applied during low power state. Hence, RF signal shall be removed before device enters low power state. After the state is switched from low power to active, there shall be at least TWK before the RF signal can be applied

Figure 10 Enter and Exit Low Power State Sequence

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com

ShenZhen ChipSourceTek Technology Co., Ltd.

### **LX8648M**

#### 0.4 to 6.0GHz SP4T Switch with MIPI

#### Reflow

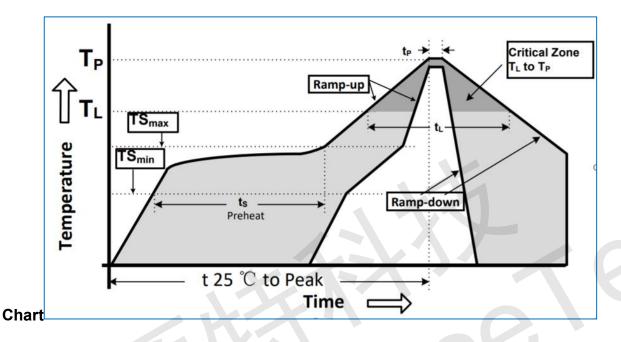

Figure 11 Recommended Lead-Free Reflow Profile

**Table 7. Reflow Chart Parameters**

| Reflow Profile                           | Parameter         |  |  |  |  |

|------------------------------------------|-------------------|--|--|--|--|

| Preheat Temperature(TSMIN to TSMAX)      | 150℃ to 200℃      |  |  |  |  |

| Preheat Time(ts)                         | 60 to 180 Seconds |  |  |  |  |

| Ramp-Up Rate(TSMAX to TP)                | 3°C/s MAX         |  |  |  |  |

| Time Above TL 217°C(tL)                  | 60 to 150 Seconds |  |  |  |  |

| Peak Temperature ( TP )                  | 260℃              |  |  |  |  |

| Time within 5℃ of Peak Temperature(tP)   | 20 to 40 Seconds  |  |  |  |  |

| Ramp-Down Rate(TSMAX to TP)              | 6℃/s MAX          |  |  |  |  |

| Time for 25℃ to Peak Temperature(t25-TP) | 8 Minutes MAX     |  |  |  |  |

#### **ESD Sensitivity**

Integrated circuits are ESD sensitive and can be damaged by static electric charge. Proper ESD protection techniques should be applied when devices are operated.

#### **RoHS Compliant**

This product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) and polybrominated diphenyl ethers (PBDE), and are considered RoHS compliant.

TEL: +86-0755-27595155 27595165

FAX: +86-0755-27594792

WEB:Http://www.ChipSourceTek.com