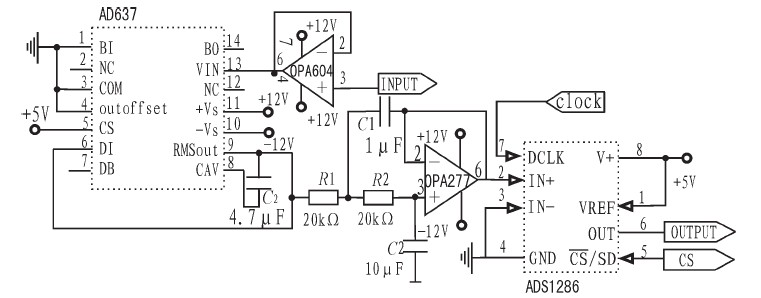

The true RMS detection chip AD637 is used in the power measurement circuit to detect the true RMS of the signal, which is then sampled by the 12 bit serial interface and the 20 kHz sampling rate ad chip ads1286 and then sent to the FPGA for processing by the program to calculate the power and display it. As shown in Figure 6.

Fig. 6 power measurement and display circuit

An emitter follower composed of opa604 has reached the function of isolating the front and rear stages. Changing the value of the average capacitance can set the average time constant and determine the low-frequency accuracy, the size of the output ripple and the stability time. The AC ripple component can be reduced by increasing the value of this capacitance, but this will increase the establishment time. Therefore, the method followed by a second-order active low-pass filter is selected to reduce the output ripple. After the true RMS is obtained, it is directly sent to ads1286 for analog-to-digital conversion, and then processed by FPGA to calculate the output power of the system and display it.

4 Design of system software

According to the requirements of the topic, in order to realize the measurement and display function of the system power, the hardware adopts 8-bit CPU AT89S52, which is realized by C51 programming. The single chip microcomputer GUI should complete the functions of controlling ads1286, collecting data, calculating power and sending display. FPGA (ep1c6qc240 of cyclone series of ATERA company) is used as a bus controller to manage the data exchange between LCD and a / D and MCU. Using Verilog HDL language in quartus9 1 environment.

5 test methods and results

1 5 MHz function signal generator model: Agilent 33120A

Digital oscilloscope model: Tektronix TDS 1002, dual channel, 60 MHz

DC power model: sg173sb3, voltage and current stabilizing type

Four and a half digit multimeter model: fluke 45 dual display multimeter

5.2 test scheme and result analysis

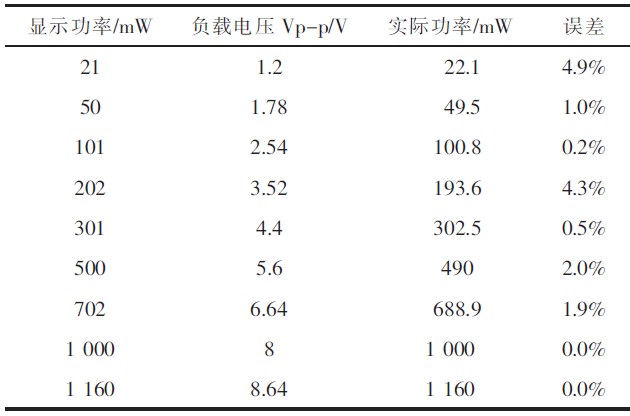

1) The Agilent signal source is used to give the input audio signal for power display error measurement. The oscilloscope measures the voltage peak VO on the load at the single end output test point, calculates the actual power according to the formula, and then calculates the display error. The results are shown in Table 1.

Table 1 test data of passband performance of amplification circuit

It can be seen from the data in the table that the system power display module has 4-digit digital display, the accuracy is better than 5%, and the error is small.

2) For noise, the Agilent signal source is used to give the input audio signal (ensure that the signal frequency is below 20 kHz), and 0.1 μ F capacitor for AC short circuit between input end and ground, and measure the noise at output end with oscilloscope. At this time, the measured noise is 2.96mv

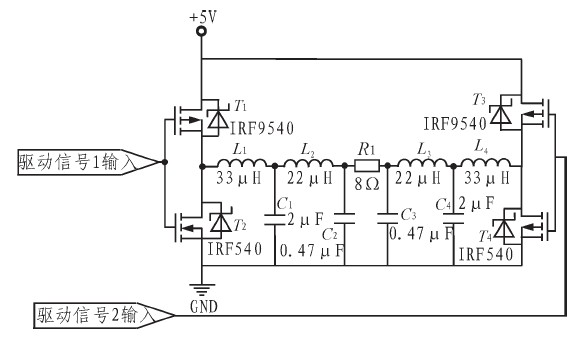

3) The efficiency measurement uses the DC power supply to supply power to the power amplifier circuit separately, so as to test the efficiency. The power supply voltage is + 5 v. the input signal is given in the same way as the passband. Observe the amplitude of the output signal with an oscilloscope, adjust the output to 200 MW and 500 MW, string the four and a half digit multimeter into the amplifier circuit, and measure the circuit current I. calculate the efficiency of the power amplifier according to the formula. The results are shown in Table 2.

Table 2 efficiency test data of power amplifier circuit

It can be seen from the table that when the output power is 500MW, the efficiency of the power amplification circuit is as high as 64.10%, which greatly meets the requirements of the subject; When the output is 200 MW, the efficiency also reaches 43.96% The system can realize high-efficiency audio amplification.

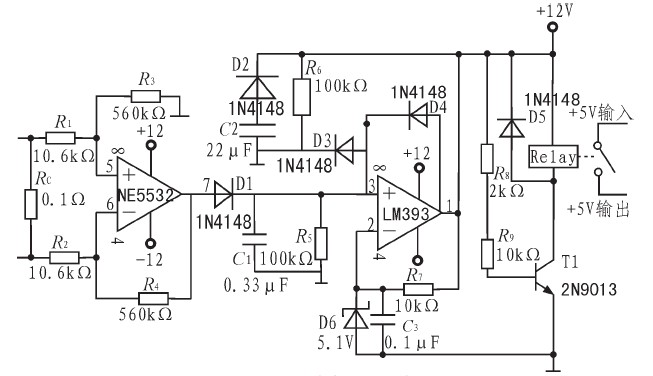

4) The overcurrent protection measurement gives the input signal in the same way as the passband measurement. Observe the amplitude of the output signal with an oscilloscope and short circuit both ends of the load. It can be seen that the warning light of the short circuit module is on, the power supply of the power amplification part is cut off and the output becomes zero, so as to achieve the purpose of protection.

6 Conclusion

The system realizes the amplification and processing of audio signal, and completes the functions of high-efficiency power amplification, signal transformation, power measurement and display, overcurrent protection and so on. The system has good performance and high indexes in power and efficiency. Amplification circuit, signal transformation, power measurement and short-circuit protection have received good results. Especially in terms of power, it can reach 1.16 W, the efficiency can reach 64%, the noise is very low, and the display error of power measurement is small. Simple operation and flexible human-computer interaction.

|

Disclaimer: This article is transferred from other platforms and does not represent the views and positions of this site. If there is infringement or objection, please contact us to delete. thank you!

中恒科技ChipHomeTek

|